chatgpt专题

其他

数学建模

信号维度

技术群

list

supervisor

信号量

流媒体

学习方法

illustrator

期末考试

android入门

电机控制

素质模型

dp

总体设计

torch

高频交易

模型转换

ZYNQ

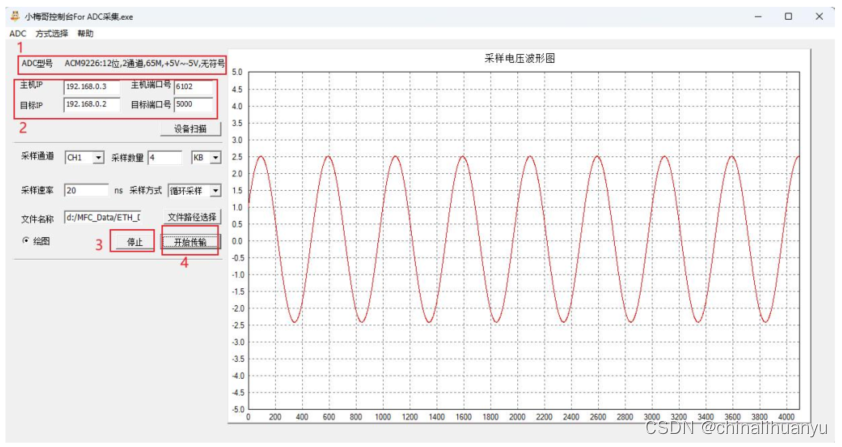

2024/4/11 15:55:39Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(三)

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(前导)

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(一)

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(二) 八、板级验证

1.验证内容

通过电脑…

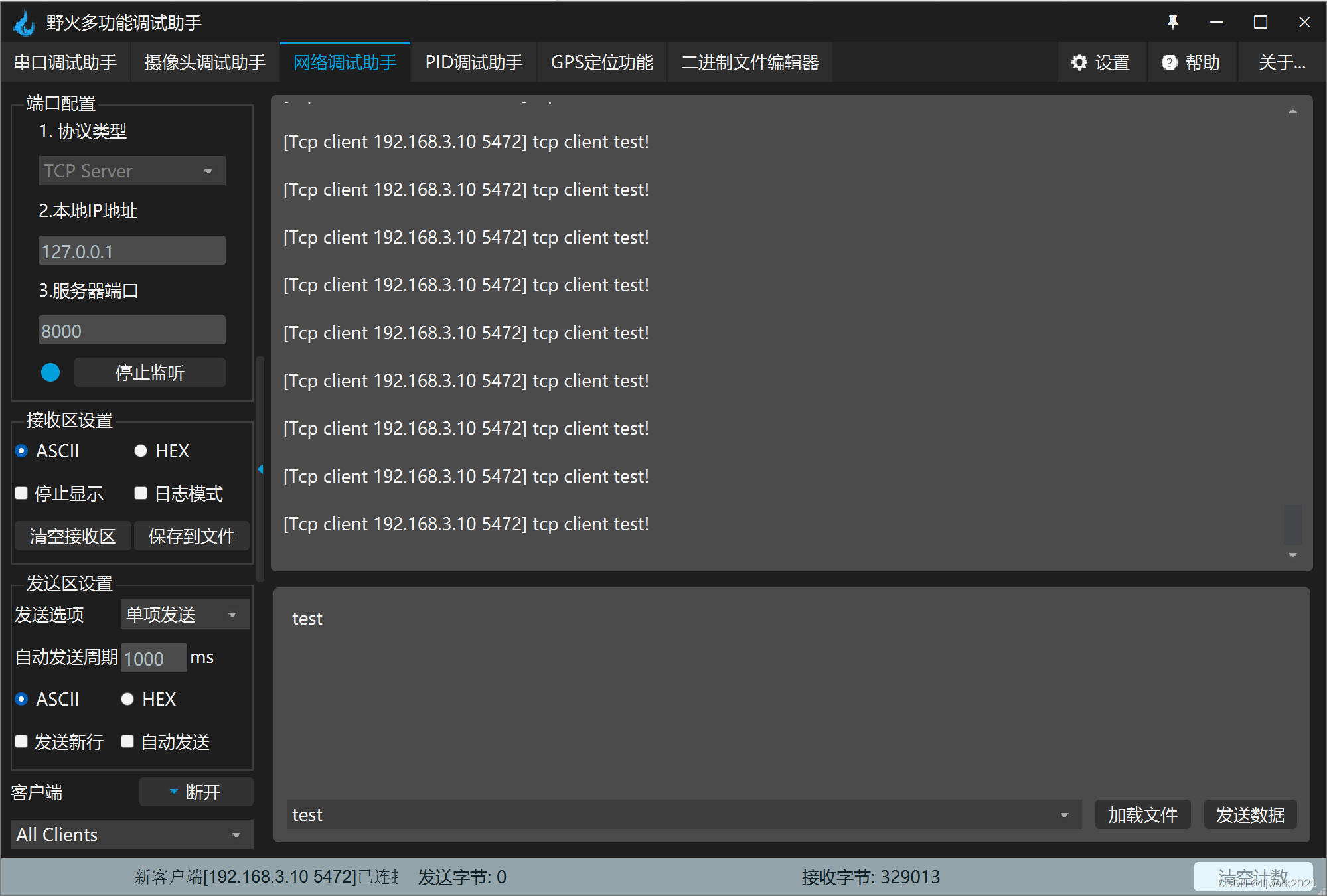

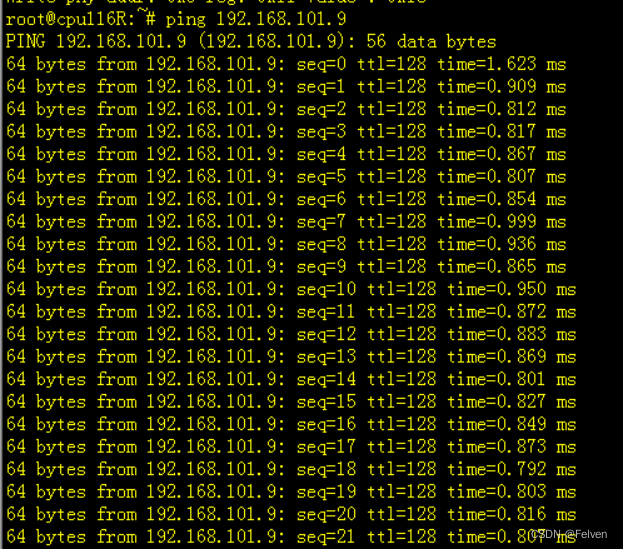

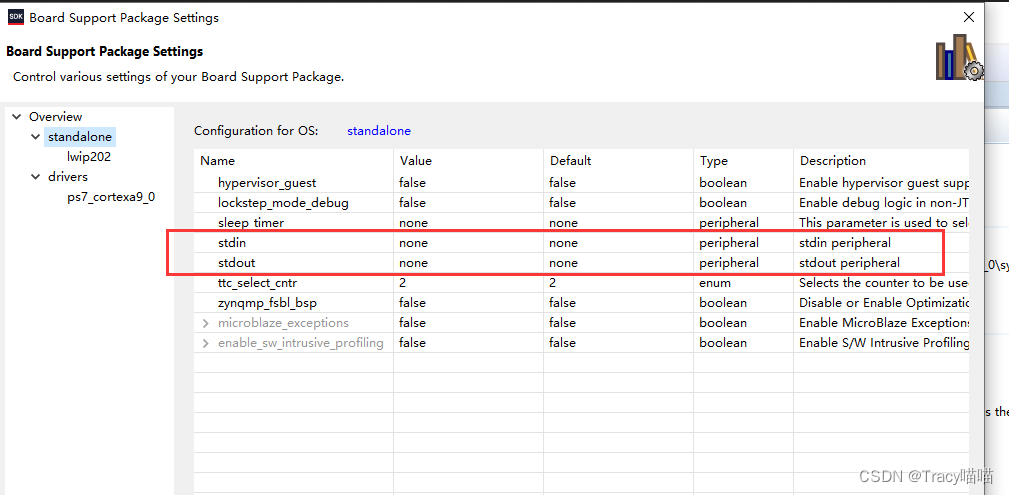

ZYNQ连载08-Lwip网络组件

ZYNQ连载08-Lwip网络组件

1. 添加Lwip包 2. Lwip配置

我这里关闭ipv6和dhcp。

3. tcp客户端

#include "include/my_tcp.h"

#include "lwip/ip.h"#define THREAD_STACKSIZE 1024

#define SERVER_PORT 8000

#define SERVER_ADDR "192.168.3.190&qu…

Xilinx Zynq-7000系列FPGA多路视频处理:图像缩放+视频拼接显示,提供工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐FPGA图像处理方案FPGA图像缩放方案FPGA视频拼接叠加融合方案推荐 3、设计思路详解HLS 图像缩放介绍Video Mixer介绍 4、vivado工程介绍PL 端 FPGA 逻辑设计PS 端 SDK 软件设计 5、工程移植说明vivado版本不一致处理FPGA型号不一致处理其他…

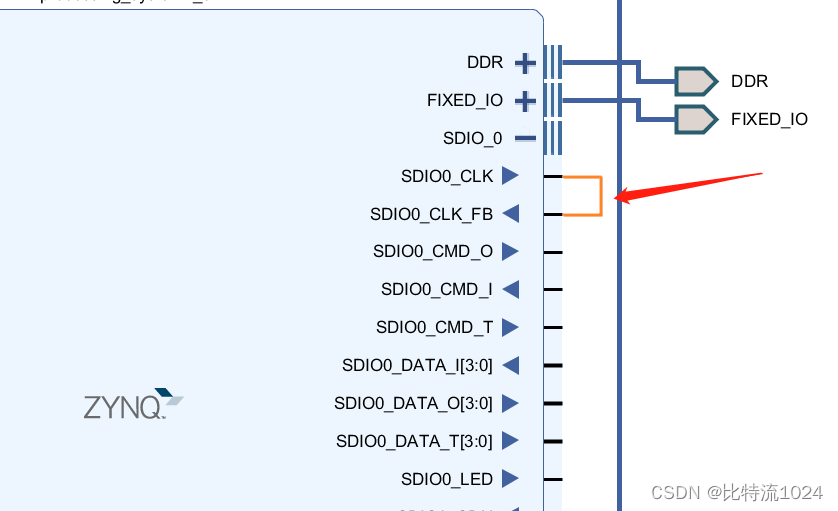

zynq emio 外接emmc/SD 相关问题与描述总结

在使用emio的情况要注意,由于通过PL的扩展,导致一些问题,如时钟时序,数据、cmd的方向控制都需要注意。

A、emio的clk和clk_fb要短接(原因是要通过反馈修复clk输出时序),可通过内部直接短接&…

基于ZYNQ+linux+xenomai 的多轴运动控制平台关键技术研发-测试系统搭建(四)

本章搭建实验测试平台,对多轴运动控制平台的硬件功能和系统任务通信功能 进行测试。通过测试结果,进行平台硬件设计正确性验证和系统实时处理与同步控制 的功能与性能验证。 5.1 测试平台搭建 多轴运动控制系统的测试平台搭建如图 5.1 所示。测试平台由安…

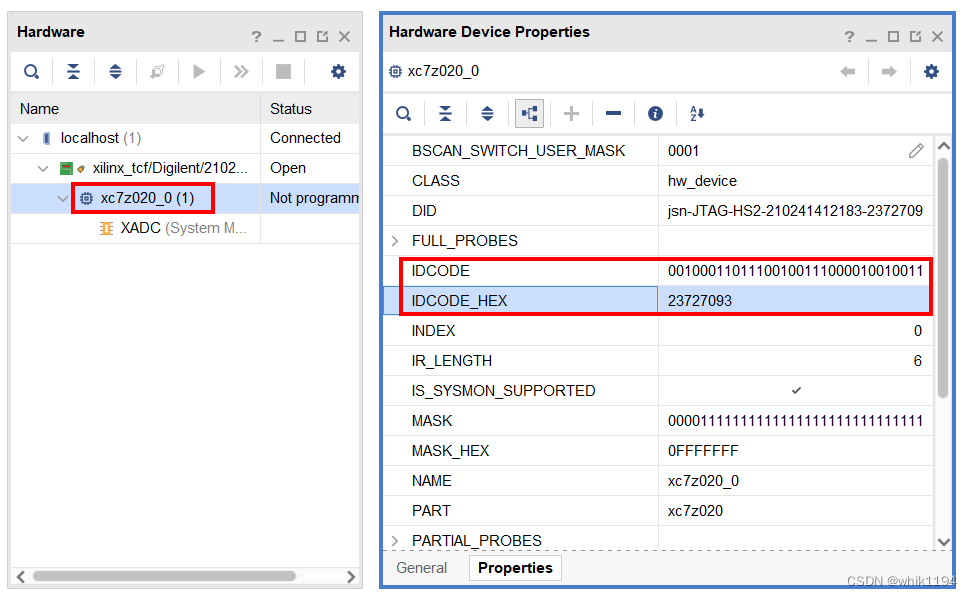

Xilinx ZYNQ系列10款型号IDCODE汇总(2023年7月最新版)

ZYNQ系列产品选型手册:zynq-7000-product-selection-guide

/* Zynq Devices. */

#define IDCODE_XC7Z007 0x03723093

#define IDCODE_XC7Z010 0x03722093

#define IDCODE_XC7Z012 0x0373C093

#define IDCODE_XC7Z014 0x03728093

#defi…

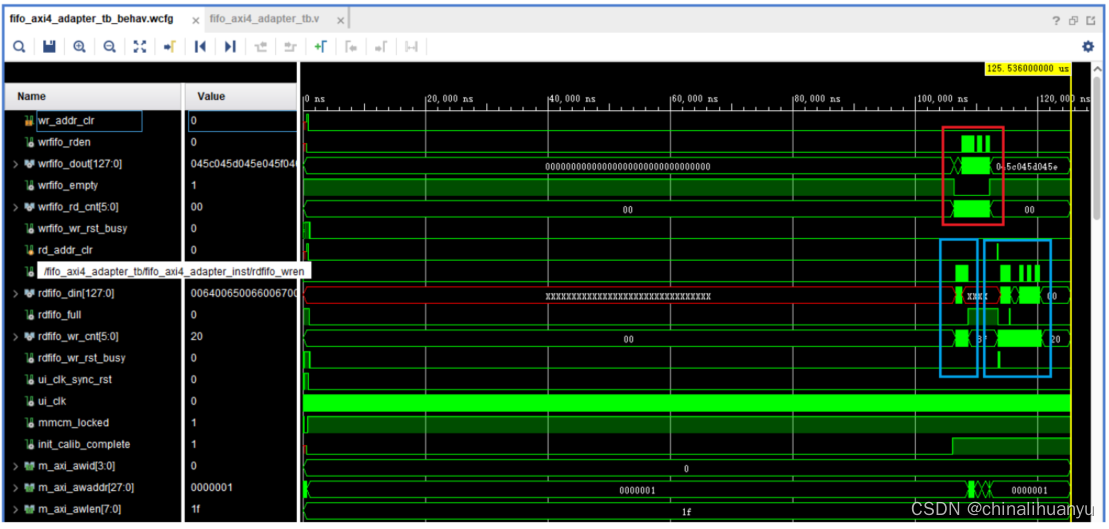

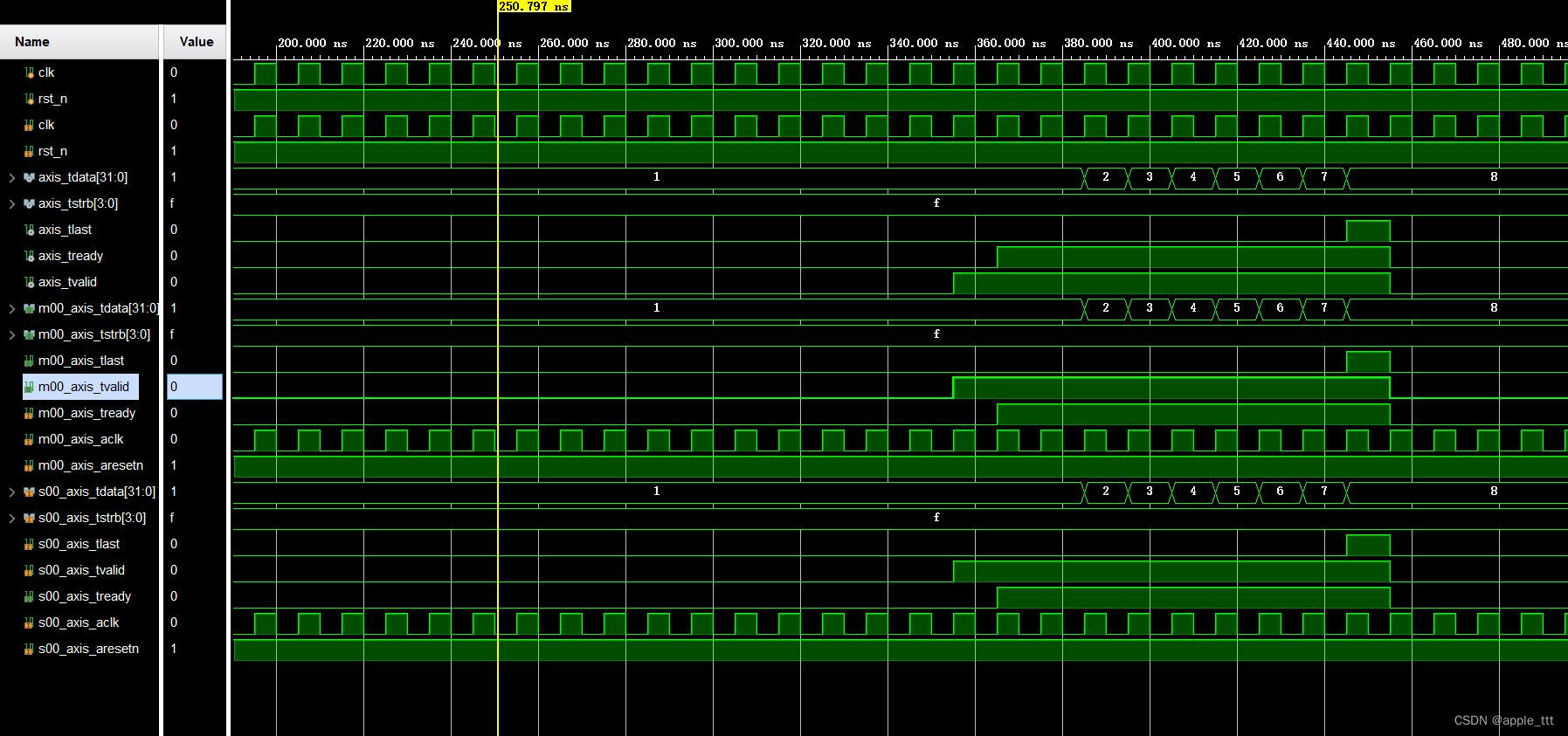

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(一)

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(前导) 四、AXI转FIFO接口模块设计

1.AXI接口知识

AXI协议是基于 burst的传输,并且定义了以下 5 个独立的传输通道:

读地址通道(Read Address Channel, …

procise纯PL流程点灯记录

procise纯PL流程点灯记录

一、概述

此篇记录使用procise工具构造JFMQL15T 纯PL工程,显示PL_LED闪烁; 硬件说明如下: 时钟引脚 Pl_CLK: U2 ,IO_L14P_T2_SRCC_34 PL_LED1 : E2, IO_L17P_T2_AD5P_35 PL_LED2: D6, IO_L2N_T0_AD8N_35 PL_LED3 :…

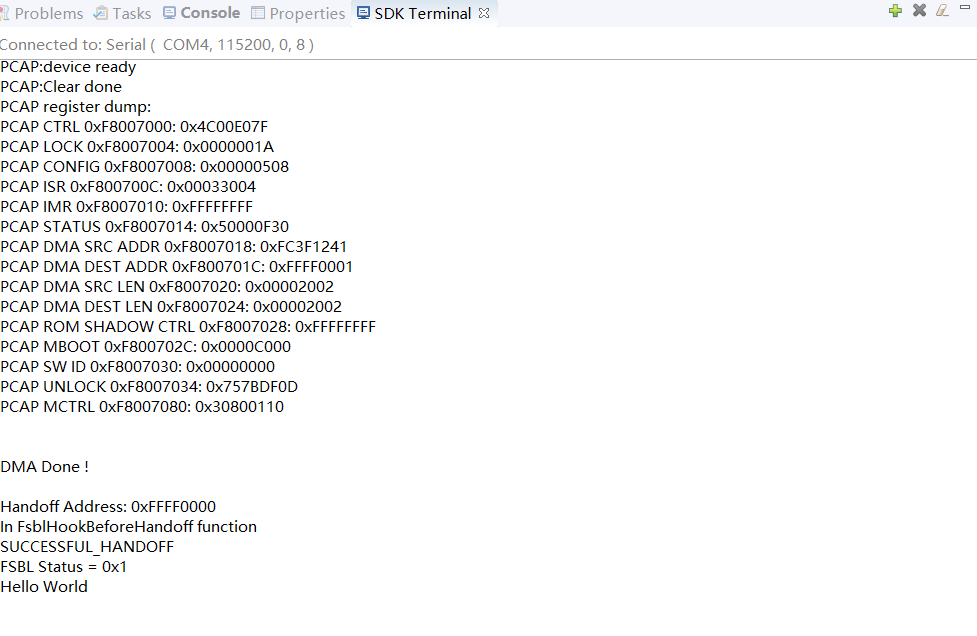

江山易改本性难移之ZYNQ SDK FSBL加载启动代码详解

SDK版本:2018.3

写在前面:

该文档不足以使你清楚FSBL启动的寄存器级的操作细节,但可以让你看明白整个ZYNQ7000 FSBL代码执行的主要流程。

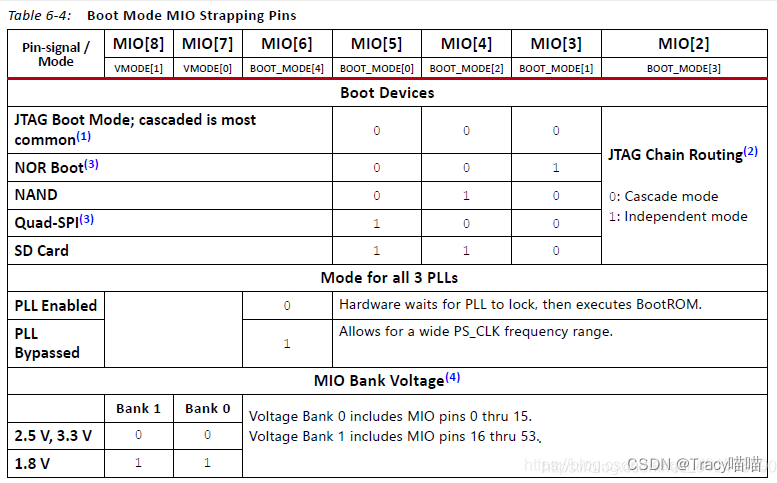

1. ZYNQ7000加载启动流程 (1)BootRom阶段为ARM上电后最早加载的代码&#x…

ZYNQ之HLS学习----开篇实验

1 Vivado HLS简介

Xilinx 推出的 Vivado HLS 工具可以直接使用C、C或 System C 来对 Xilinx 系列的 FPGA 进行编程

FPGA 设计中从底层向上一共存在着四种抽象层级,依次为:结构性的、RTL、行为性的和高层

Vivado HLS 的功能简单地来说就是把 C、C 或 S…

【IC设计】ZC706板卡点灯入门(含Verilog代码,xdc约束,实验截图)

文章目录 假定已知的前置知识需求:注意点:代码实现:顶层模块led闪烁模块xdc约束 这篇博客将针对AMD Zynq 7000 SoC ZC706 Evaluation Kit板卡(对应Vivado创建工程时FPGA型号:XC7Z045ffg900-2)实现基本的点灯程序。 假定已知的前置…

ZYNQ连载01-ZYNQ介绍

ZYNQ连载01-ZYNQ介绍

1. ZYNQ

参考文档:《ug585-zynq-7000-trm.pdf》

ZYNQ分为PS和PL两大部分,PS即ARM,PL即FPGA,PL作为PS的外设。

2. 方案

ZYNQ7020为双核A9架构,多核处理器常用的运行模式为AMP(非对称多处理)和…

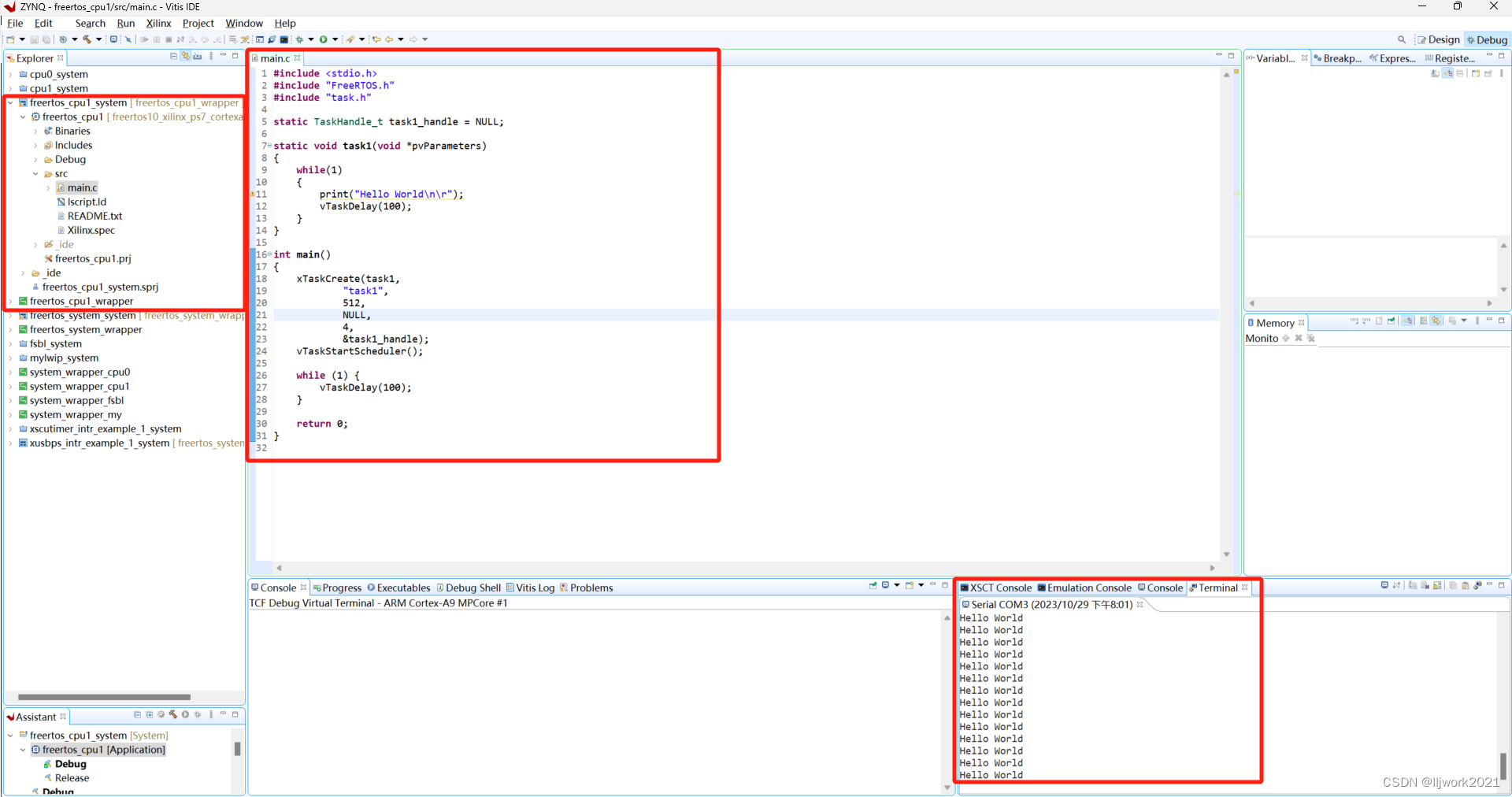

ZYNQ连载04-Vitis创建FreeRTOS工程

ZYNQ连载04-Vitis创建FreeRTOS工程

1. 创建工程 2. 测试程序

#include <stdio.h>

#include "FreeRTOS.h"

#include "task.h"static TaskHandle_t task1_handle NULL;static void task1(void *pvParameters)

{while(1){print("Hello World\n\…

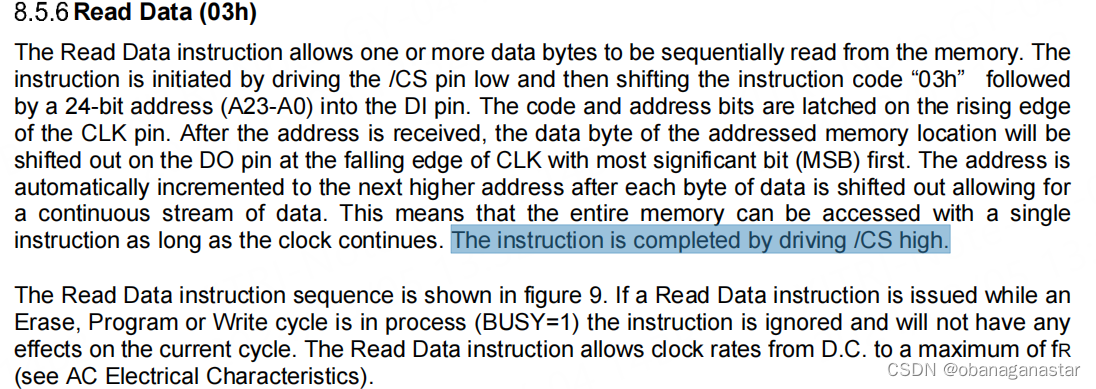

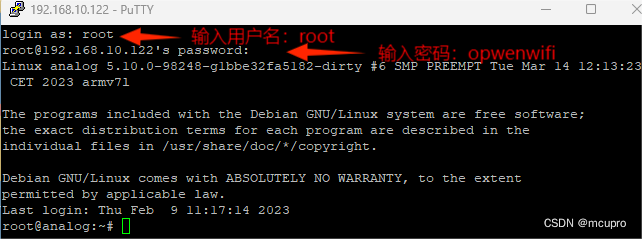

基于ZYNQ PS-SPI的Flash驱动开发

本文使用PS-SPI实现Flash读写,PS-SPI的基础资料参考Xilinx UG1085的文档说明,其基础使用方法是,配置SPI模式,控制TXFIFO/RXFIFO,ZYNQ的IP自动完成发送TXFIFO数据,接收数据到RXFIFO,FIFO深度为12…

基于ZCU106平台部署Vitis AI 1.2/2.5开发套件【Vivado+Vitis+Petalinux2020/2022】

Vitis AI是 Xilinx 的开发平台,适用于在 Xilinx 硬件平台(包括边缘设备和 Alveo 卡)上进行人工智能算法推理部署。它由优化的IP、工具、库、模型和示例设计组成。Vitis AI以高效易用为设计理念,可在 Xilinx FPGA 和 ACAP 上充分发…

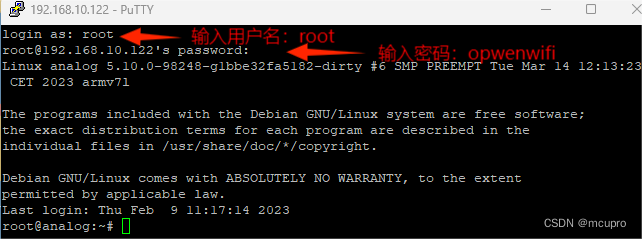

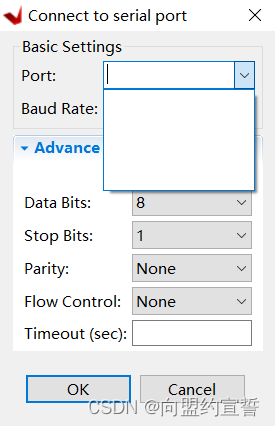

zedboard+AD9361 运行 open WiFi

先到github上下载img,网页链接如下:

https://github.com/open-sdr/openwifi?tabreadme-ov-file

打开网页后下载 openwifi img 用win32 Disk lmager 把文件写入到SD卡中,这一步操作会把SD卡重新清空,注意保存数据。这个软件我会…

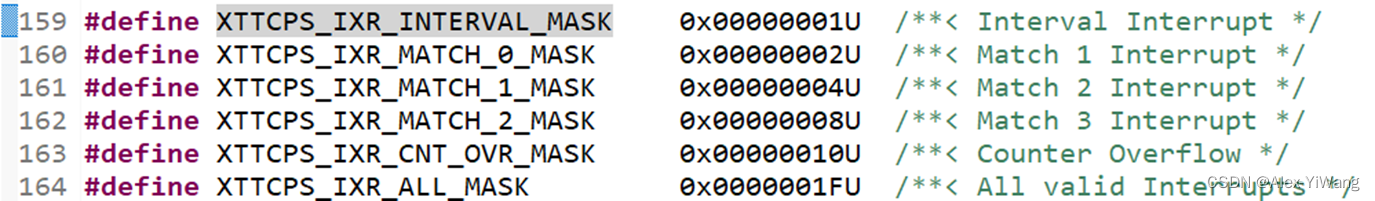

ZYNQ:【1】深入理解PS端的TTC定时器(Part1:原理+官方案例讲解)

碎碎念:好久不见,甚是想念!本期带来的是有关ZYNQ7020的内容,我们知道ZYNQ作为一款具有硬核的SOC,PS端很强大,可以更加便捷地实现一些算法验证。本文具体讲解一下里面的TTC定时器,之后发布的Part…

复旦微裸机SD卡移植

Demo下的FatFs整个拷贝至BSP->librc下,不要和FSBL下的混了!!!!! 将头文件添加到编译环境 sdmmcps_v1_0整个替换

BootLoader下cache.c和cache.h替换 编译报错如下:

报错如下,…

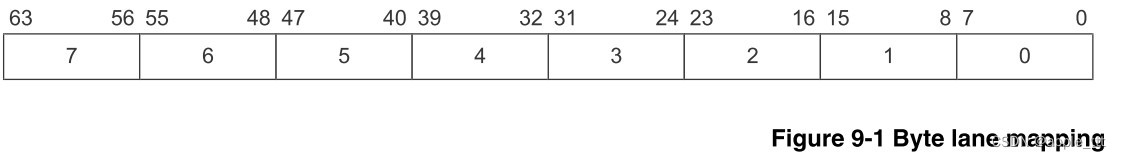

【ZYNQ】AXI4总线接口协议学习

建议翻看着底部的参考文档资料和本文一起辅助阅读 本文带你详细的了解AXI总线协议,并且基于官方手册,能够提高你的手册阅读能力。 什么是AXI

AXI 的英文全称是 Advanced eXtensible Interface,即高级可扩展接口,它是 ARM 公司所提…

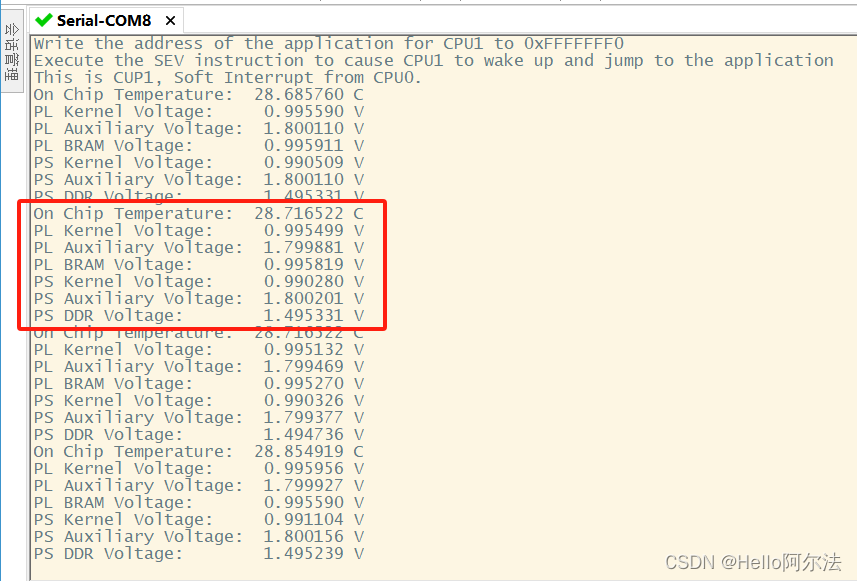

【ZYNQ】ZYNQ7000 XADC 及其驱动示例

XADC 简介

ZYNQ SoC 的 XADC 模块包括两个 12 位的模数转换器,转换速率可以达到 1MSPS(每秒一百万次采样)。它带有片上温度和电压传感器,可以测量芯片工作时的温度和供电电压。

在 7 系列的 FPGA 中,XADC 提供了 JTA…

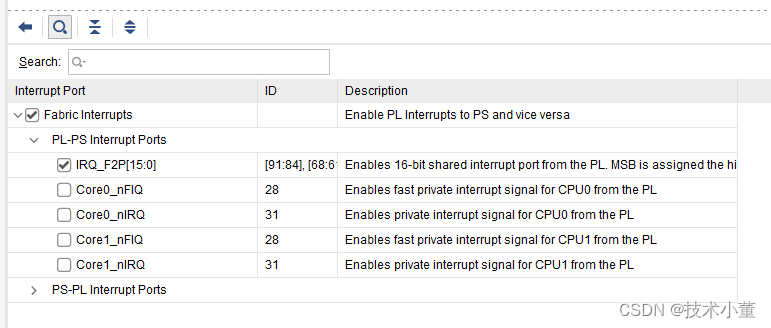

ZYNQ PL 中断请求

1 中断概念 中断学习

2 ZYNQ 中断框图 上图为 zynq 中断分布框图。可以看到部分 PL 到 PS 部分的中断,经过中断控制分配器(ICD), 同时进入 CPU1 和 CPU0。查询下面表格,可以看到 PL 到 PS 部分一共有 20 个中断可以使…

Xilinx Zynq-7000系列FPGA实现视频拼接显示,提供两套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐FPGA图像处理方案FPGA视频拼接叠加融合方案推荐 3、设计思路详解Video Mixer介绍 4、工程代码1:2路视频拼接 HDMI 输出PL 端 FPGA 逻辑设计PS 端 SDK 软件设计 5、工程代码2:4路视频拼接 HDMI 输出PL 端 FPGA 逻辑设…

一起学习用Verilog在FPGA上实现CNN----(二)卷积层设计

1 打开Vivado工程

Vivado工程文件如图: 打开Vivado软件,打开工程,如图: 自动升级到当前版本,如图: 暂时选择现有开发板的型号,如图: 出现一条警告性信息,暂时先不管&…

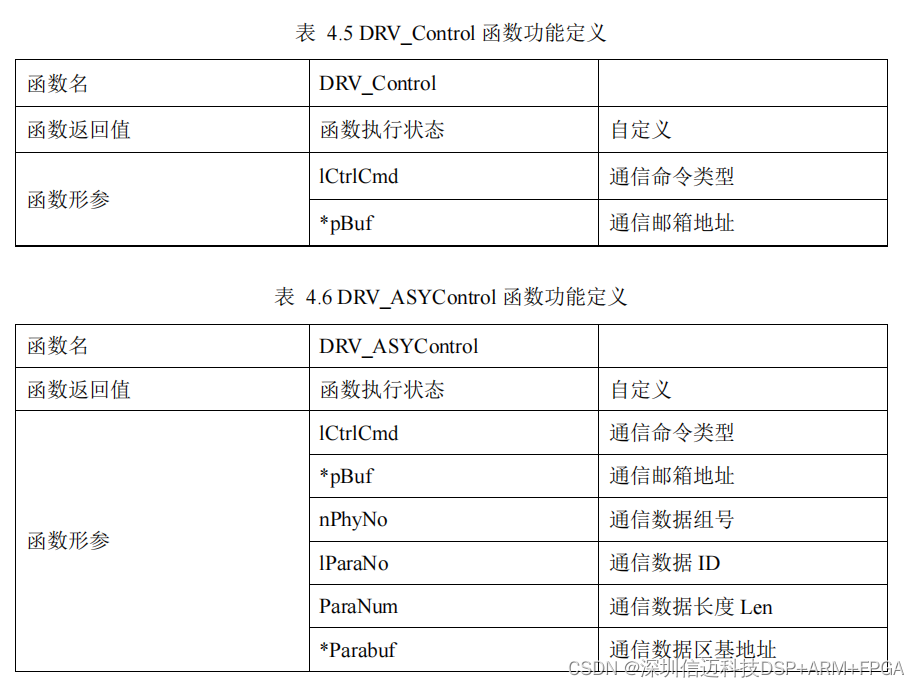

基于ZYNQ 的多轴运动控制平台关键技术研发-Linux+xenomai开源实时系统设计(二)

4. SoC 双核系统与核间多任务通信设计 本章详细介绍 AMP 架构下 SoC 核系统的设计和核间任务通信的实现方法。首 先,进行双核系统的搭建并完成设备驱动的移植;然后,进行基于共享内存的通信模 块设计;最后,针对系统不同…

Zynq非VDMA方案实现视频3帧缓存输出,无需SDK配置,提供工程源码和技术支持

目录1、前言2、VDMA的不便之处3、FDMA取代VDMA实现视频缓存输出4、Vivado工程详解5、上板调试验证并演示6、福利:工程代码的获取1、前言

对于Zynq和Microblaze的用户而言,要想实现图像缓存输出,多半要使用Xilinx推荐的VDMA方案,该…

ZYNQ - 无DDR固化程序(代码运行在OCM上)

写在前面

ZYNQ固化时,正常情况下都需要DDR参与,但是有时硬件设计时,可能将DDR去掉或设计出错,这将导致ZYNQ无法正常固化,之前有写过一个使用静态链接库进行无DDR固化的文章,当时那个是压缩了FSBL的相关代码…

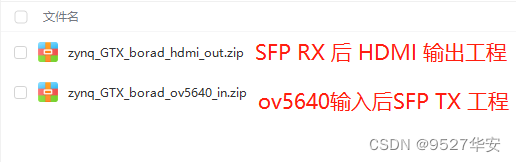

Zynq GTX全网最细讲解,aurora 8b/10b协议,OV5640板对板视频传输,提供2套工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 GT 高速接口解决方案3、GTX 全网最细解读GTX 基本结构GTX 发送和接收处理流程GTX 的参考时钟GTX 发送接口GTX 接收接口GTX IP核调用和使用 4、设计思路框架视频源选择OV5640摄像头配置及采集动态彩条视频数据组包GTX aurora 8b/10b数据对…

ZYNQ EMIO MIO

1 概述

先来了解GPIO的BANK分布,在UG585文档GPIO一章中可以看到GPIO是有4个BANK, 注意与MIO的BANK区分。 BANK0 控制32个信号,BANK1控制22个信号,总共是MIO的54个引脚,也就是诸如 SPI,I2C,USB,SD 等 PS 端外设接口&am…

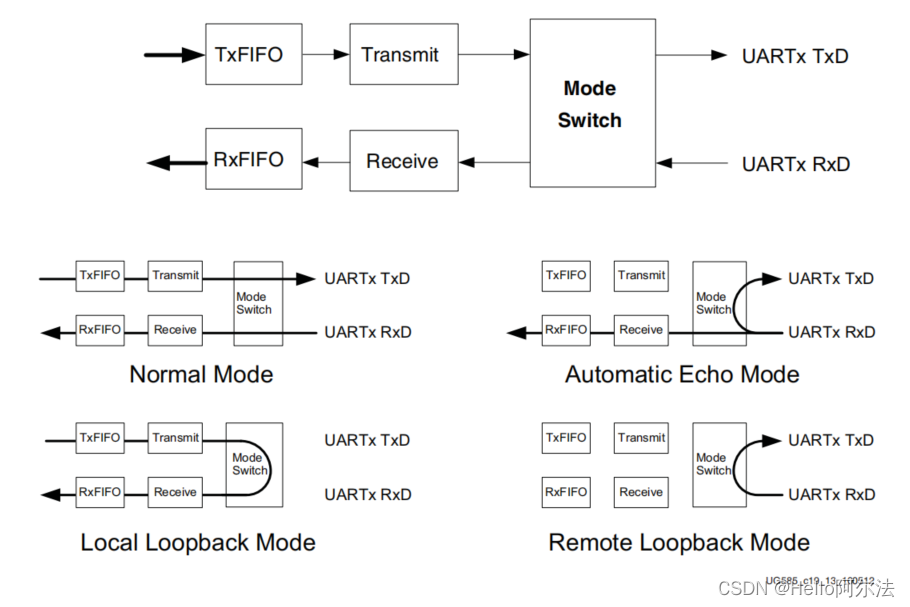

【ZYNQ】ZYNQ7000 UART 控制器及驱动示例

简介

UART 控制器介绍

UART 控制器是一个全双工异步收发控制器,ZYNQ 内部包含两个 UART 控制器,UART0 和 UART1。每一个 UART 控制器支持可编程的波特率发生器、64 字节的接收 FIFO 和发送 FIFO、产生中断、RXD 和 TXD 信号的环回模式设置以及可配置的…

ultrascale+mpsoc系列的ZYNQ中DDR4参数设置说明

ultrascalempsoc系列的ZYNQ中DDR4参数设置说明 标题1 概述标题2 讲述平台标题3 ZYNQ的DDR设置界面参数标题4 DDR参数界面说明如下 标题1 概述

本文用于讲诉ultrascalempsoc系列中的ZYNQ的DDR4的参数设置与实际硬件中的DDR选型之间的关系,为FPGA设计人员探明道路。 …

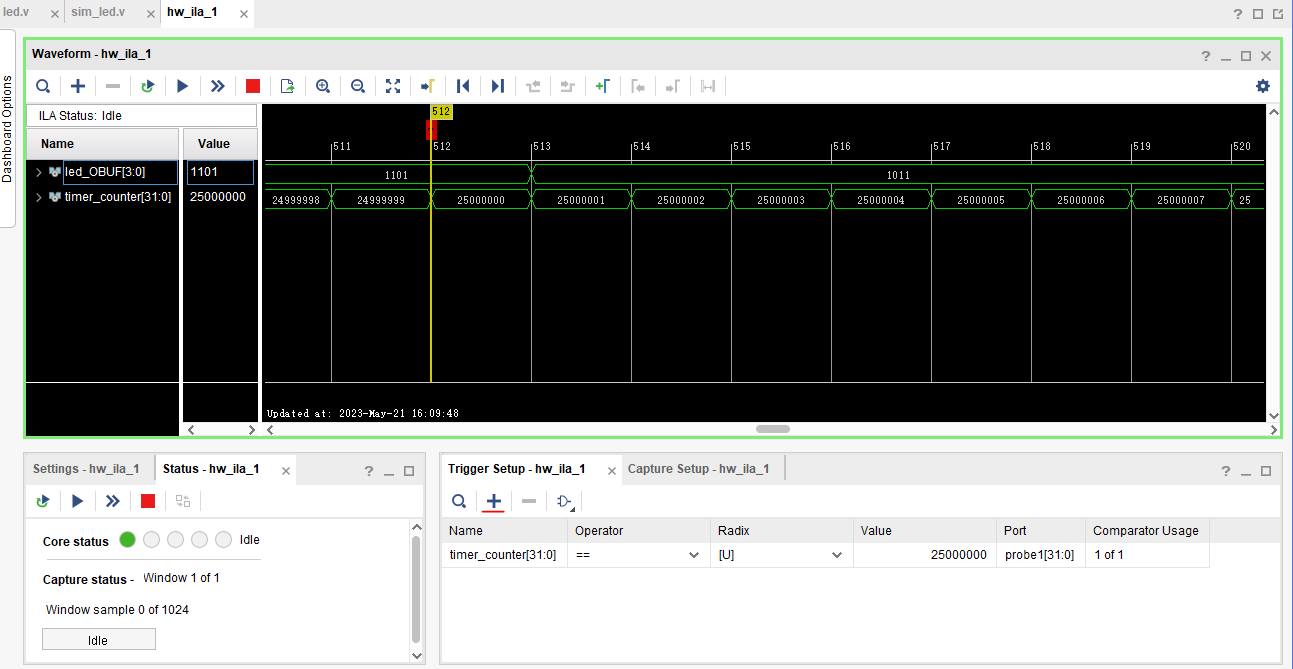

ZYNQ——PL端流水灯的实现

文章目录 一、介绍二、代码编写三、引脚分配四、仿真分析五、添加 ILA IP六、板上验证 一、介绍

本文介绍的是在ZYNQ 7020黑金开发板上实现PL端流水灯的例子,开发板上PL端的LED灯总共有4个,在原理图中找到 PL LED 如下图所示,通过看图可知&a…

Zynq-Linux移植学习笔记之66- 国产ZYNQ通过裕太PHY8521连接国产交换芯片

1、背景介绍

ZYNQ通过裕太PHY 8521主要连接两种国产交换芯片,一种为盛科的CTC8096,另一种为32所的JEM5396。框图示意如下: 2、硬件状态确认

首先检查phy的模式,确认为SGMII_MAC-RGMII_PHY 可通过读出A001寄存器确认状态 读出来应…

基于ZYNQ的移动机器人控制器设计(一)

移动机器人的设计是一个集软件、硬件、机械知识于一体的工作,因此,一套完整 方案的提出,则要展示其在机械结构、硬件架构、软件层次上的关键技术。

2.1应用场景描述和需求分析 本节首先对论文提出的移动机器人控制器方案的应用场景进行描述…

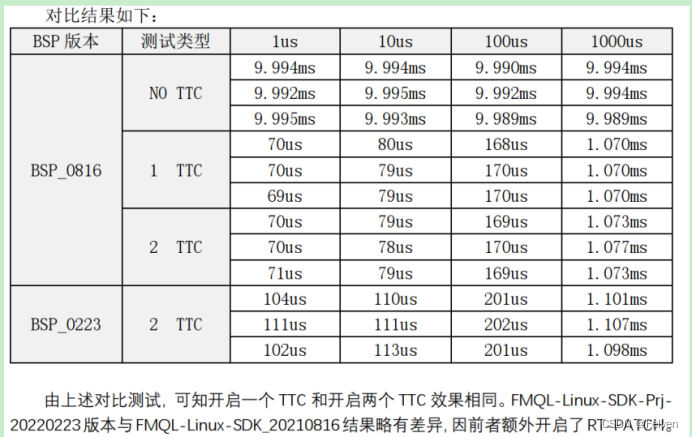

Zynq-Linux移植学习笔记之65- 国产ZYNQ在linux下usleep时间精度不准问题解决

1、背景介绍

采用复旦微的ZYNQ,跑linux操作系统,在应用程序中使用usleep进行延时时,发现存在10ms以下采用usleep试验都为10ms的情况 2、解决办法

使能设备树中的PS TTC设备,默认不是打开的

timere0024000 {compatible "s…

Zynq UltraScale+ XCZU9EG 纯VHDL解码 IMX214 MIPI 视频,2路视频拼接输出,提供vivado工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优越性4、详细设计方案设计原理框图IMX214 摄像头及其配置D-PHY 模块CSI-2-RX 模块Bayer转RGB模块伽马矫正模块VDMA图像缓存Video Scaler 图像缓存DP 输出 5、vivado工程详解PL端FPGA硬件设计…

Zynq-7000移植——根文件系统ramdisk扩容教程

参考文章:http://xilinx.eetrend.com/d6-xilinx/blog/2017-09/12036.html

前言

由于zynq 7000系列 自带的文件系统(ramdisk)大小为16M的,而我现在使用的开发板中,除去嵌入式linux系统所需要的存储空间后,…

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(前导)

ACM9238 高速双通道ADC模块自助服务手册AD9238

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(一)-CSDN博客 一、AD9238

模块在各方面参数性能上与AD9226保持一致。但是在设计上优化了信号调理电路,将单端信号先转成差分信号,…

Zynq UltraScale+ XCZU15EG 纯VHDL解码 IMX214 MIPI 视频,2路视频拼接输出,提供vivado工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优越性4、详细设计方案设计原理框图IMX214 摄像头及其配置D-PHY 模块CSI-2-RX 模块Bayer转RGB模块伽马矫正模块VDMA图像缓存Video Scaler 图像缓存DP 输出 5、vivado工程详解PL端FPGA硬件设计…

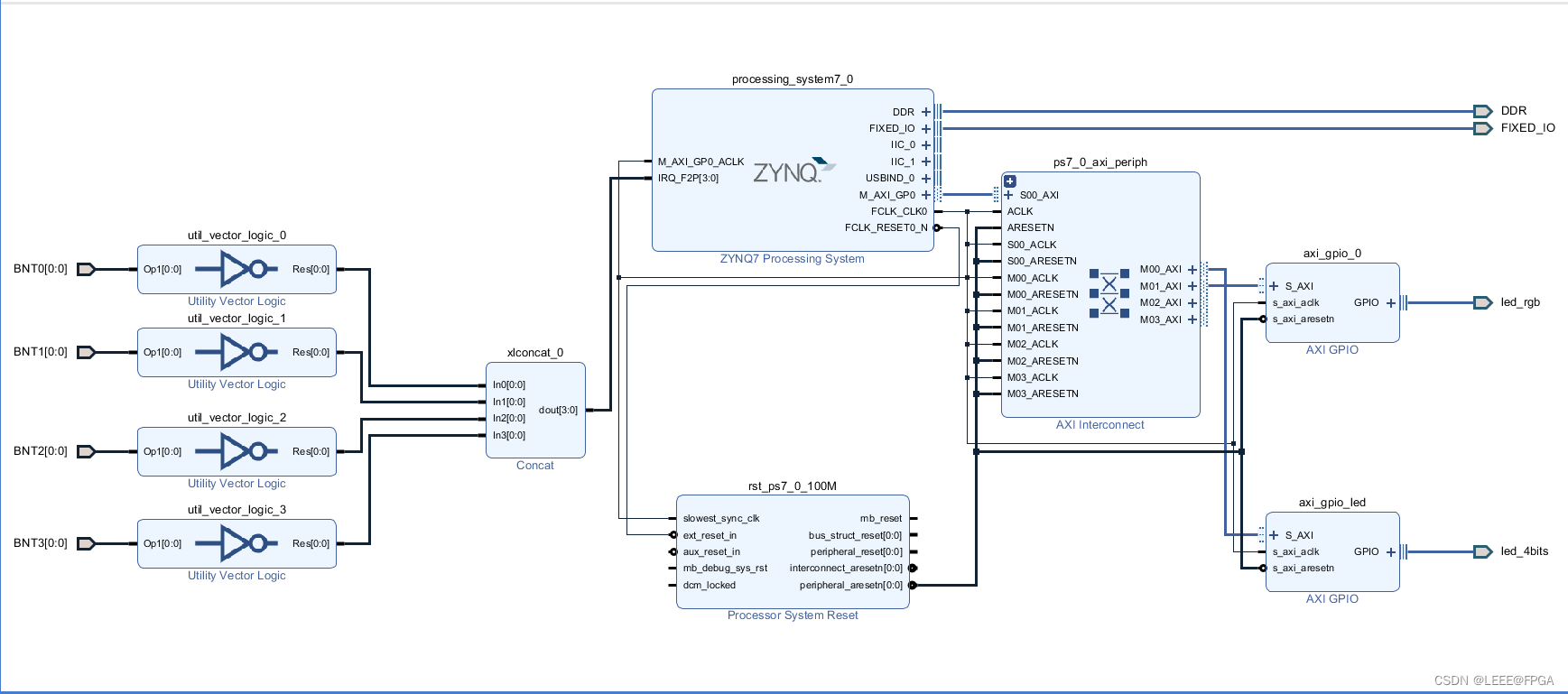

009-Zynq基操之如何去玩转PL向PS的中断(对新手友好,走过路过千万不要错过)

文章目录 前言一、PL-PS的中断是啥?二、PL-PS端中断详细步骤1.ZYNQ核配置2.PS端中断函数配置3.需要拓展多个中断函数 总结 前言

本设计跟我的ZYNQ实战合集专栏中的脉冲触发电路有关系,也正好趁这个机会讲述一下PL-PS的中断系统,如何去触发中…

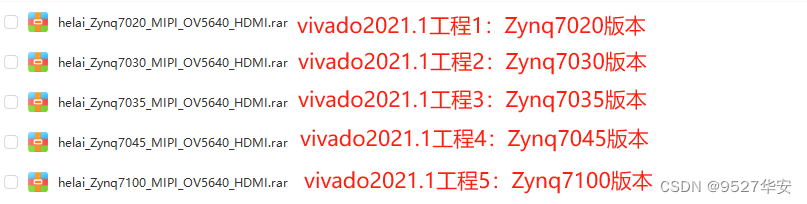

Xilinx Zynq 7000系列中端FPGA解码MIPI视频,基于MIPI CSI-2 RX Subsystem架构实现,提供5套工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优缺点4、详细设计方案设计原理框图OV5640及其配置权电阻硬件方案MIPI CSI-2 RX SubsystemSensor Demosaic图像格式转换Gammer LUT伽马校正VDMA图像缓存AXI4-Stream toVideo OutHDMI输出 5、…

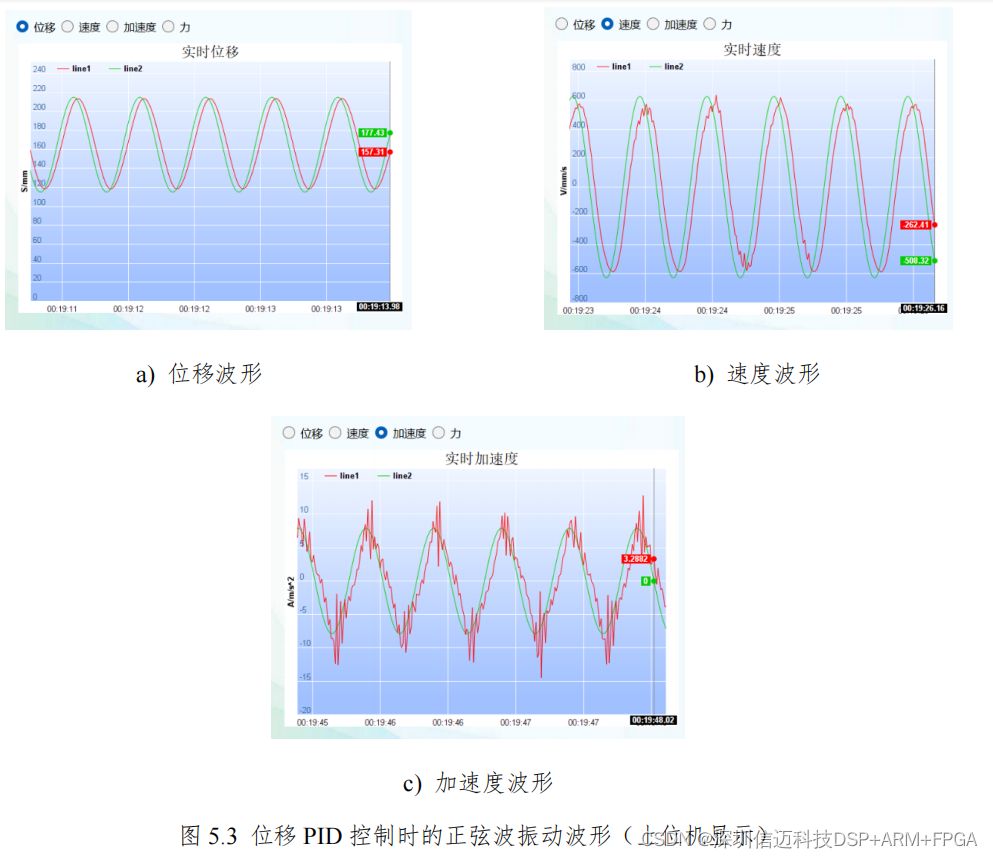

基于 Zynq+AD+DA 的振动台控制器测试与验证(四)

振动台系统测试与验证 5.1 测试平台 图 5.1 为本文使用的单自由度电液伺服振动台,其主要参数如表 5.1 所示。 5.2 数据预处理 本文所设计的控制器架构是较为通用的,运动波形可以是正弦波、随机波, 也可以是地震波。在参考波形是地震波的试验中…

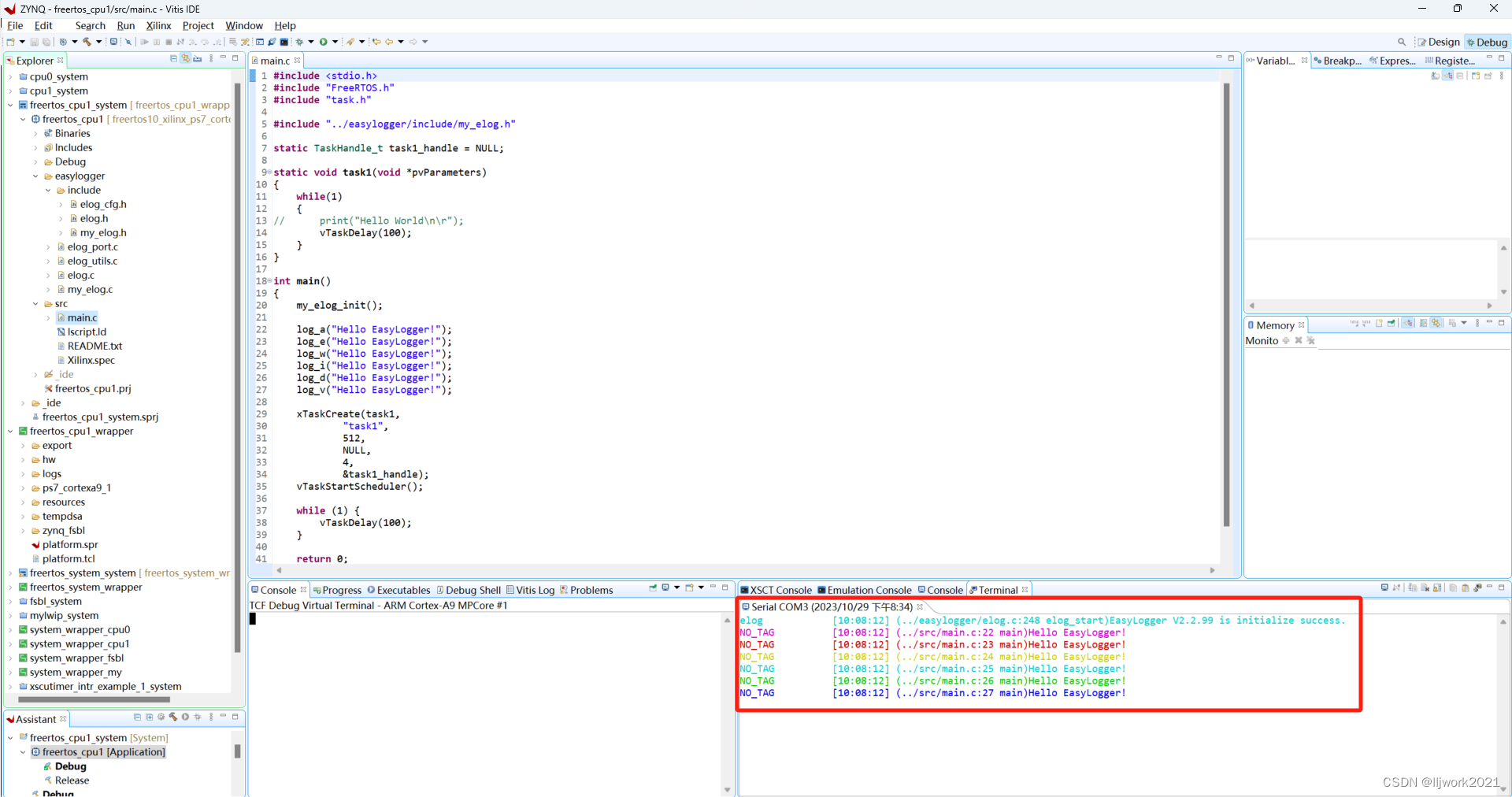

ZYNQ连载06-EasyLogger日志组件

ZYNQ连载06-EasyLogger日志组件

1. EasyLogger介绍

Easylogger仓库

2. EasyLogger移植

EasyLogger移植比较简单,在Vitis中移植时主要注意路径问题,然后适配下接口即可:

void elog_port_output(const char *log, size_t size) {printf(&…

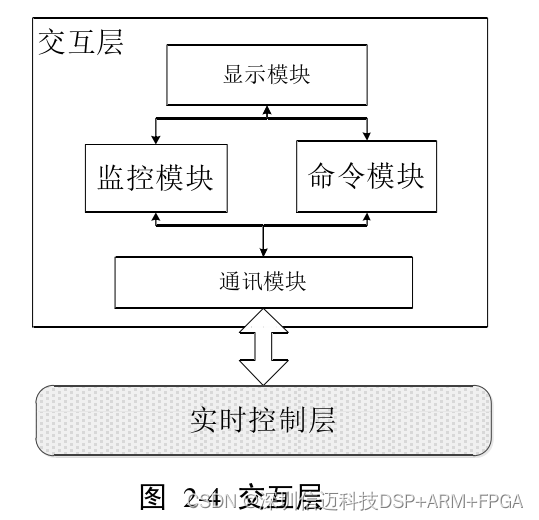

基于ZYNQ 的多轴运动控制平台关键技术研发-总体架构设计(一)

基于多轴运动控制平台的实时通信和同步控制需求,采用 Xilinx Zynq 7020 SoC 作为核心处理器,设计了双核 SoC 多轴运动控制平台的总体架构。结合多轴运动控 制系统与接口特征,完成了 SoC 运动控制平台的硬件设计,主要包括 SoC 最小…

深入浅出AXI协议(2)——通道及信号

一、前言 在之前的文章中,我们主要介绍了什么是AXI协议,AXI协议的特点与优点,然后对于AXI协议非常重要的五通道结构进行了介绍,了解了5个通道各自的作用。本文我们继续AXI协议的学习,我们将讨论5个通道的具体内容和相对…

Xilinx Zynq-7000系列FPGA任意尺寸图像缩放,提供两套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐FPGA图像处理方案FPGA图像缩放方案 3、设计思路详解HLS 图像缩放介绍 4、工程代码1:图像缩放 HDMI 输出PL 端 FPGA 逻辑设计PS 端 SDK 软件设计 5、工程代码2:图像缩放 LCD 输出PL 端 FPGA 逻辑设计PS 端 SDK 软件设…

ZCU111 BIST

内建自检(Built In Self Test)

ZCU111开发板在出厂时在Flash里已经预烧录了自检程序,所以直接参考XTP490-zcu111-quickstart.pdf(同产品附带纸质文档)进行自检即可。

自检失败

自检失败一般是因为Flash自检程序被覆…

ZYNQ之FPGA学习----RAM IP核使用实验

1 RAM IP核介绍

RAM 的英文全称是 Random Access Memory, 即随机存取存储器, 它可以随时把数据写入任一指定地址的存储单元,也可以随时从任一指定地址中读出数据,其读写速度由时钟频率决定

Xilinx 7 系列器件具有嵌入式存储器结…

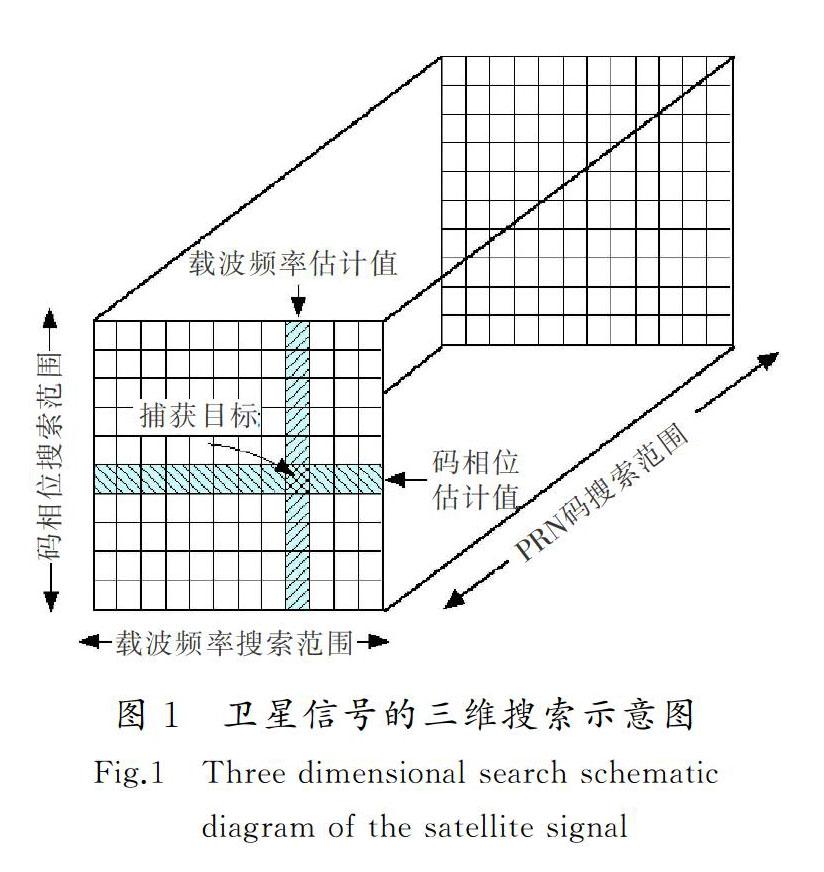

C6678/C6657+ZYNQ/K7/A7 FPGA+AD+北斗的软硬件设计方案

针对当前北斗导航定位接收机在高动态和复杂电磁环境下定位精度不高的问题,本文在了解卫星导航原理的基础上,介绍了一种基于DSPFPGA 的嵌入式北斗导航接收机的设计,以满足在高动态和复杂电磁环境下无人机、单兵、机器人等高精度导航定位的要求…

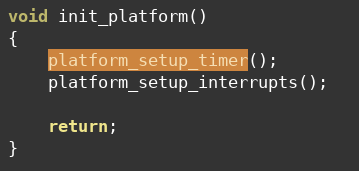

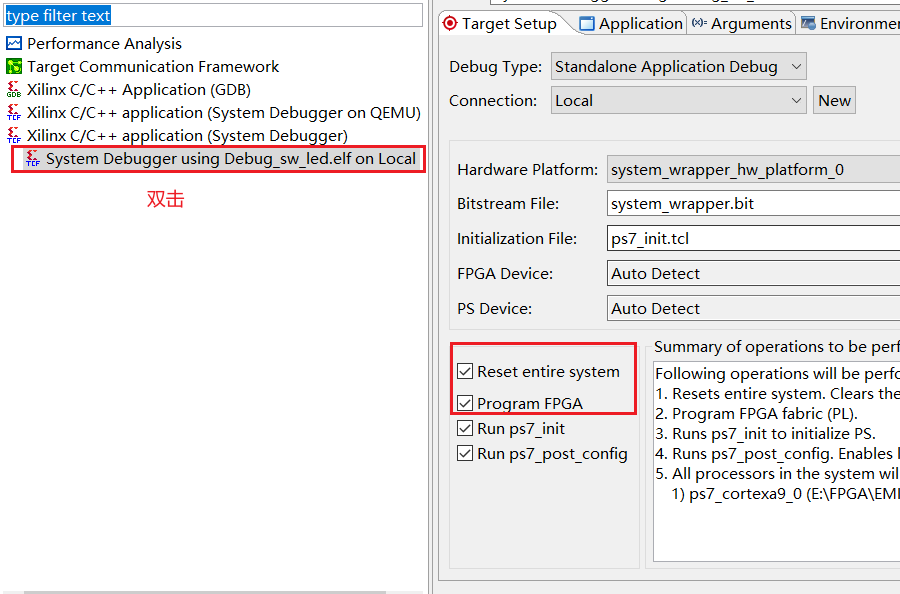

ZYNQ之嵌入式学习----开篇实验Hello World

1 ZYNQ 嵌入式系统的开篇实验Hello World

阅读本文需先学习: FPGA学习----Vivado软件使用

1.1 ZYNQ 嵌入式系统开发流程

创建Vivado工程使用IP Integrator 创建 Processor System生成顶层HDL生成比特流,导出到SDK在SDK中创建应用工程板级验证

开篇实验任务是在 …

Zynq UltraScale+ XCZU5EV 纯VHDL解码 IMX214 MIPI 视频,2路视频拼接输出,提供vivado工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优越性4、详细设计方案设计原理框图IMX214 摄像头及其配置D-PHY 模块CSI-2-RX 模块Bayer转RGB模块伽马矫正模块VDMA图像缓存Video Scaler 图像缓存DP 输出 5、vivado工程详解PL端FPGA硬件设计…

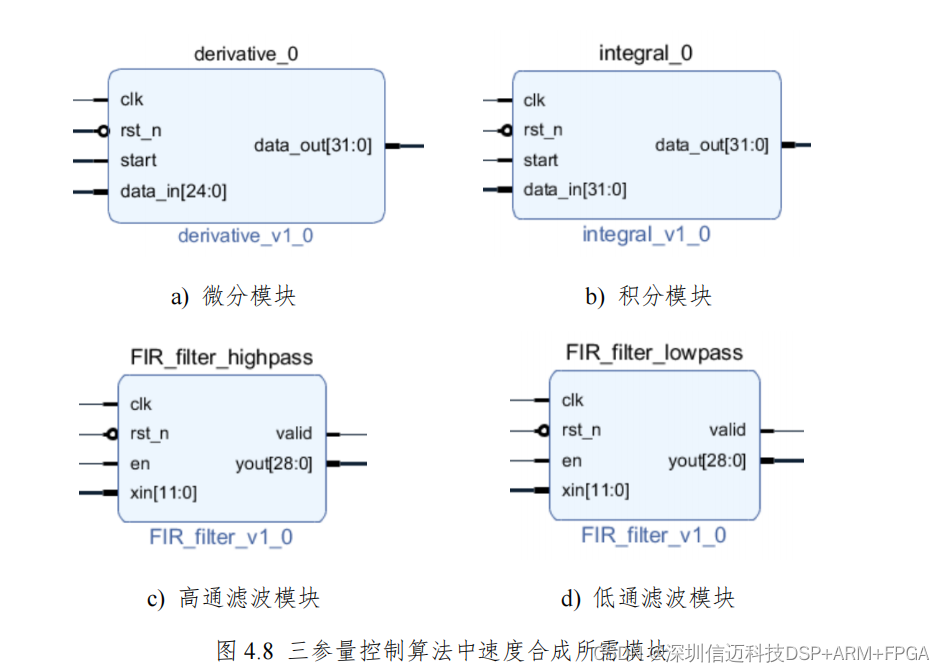

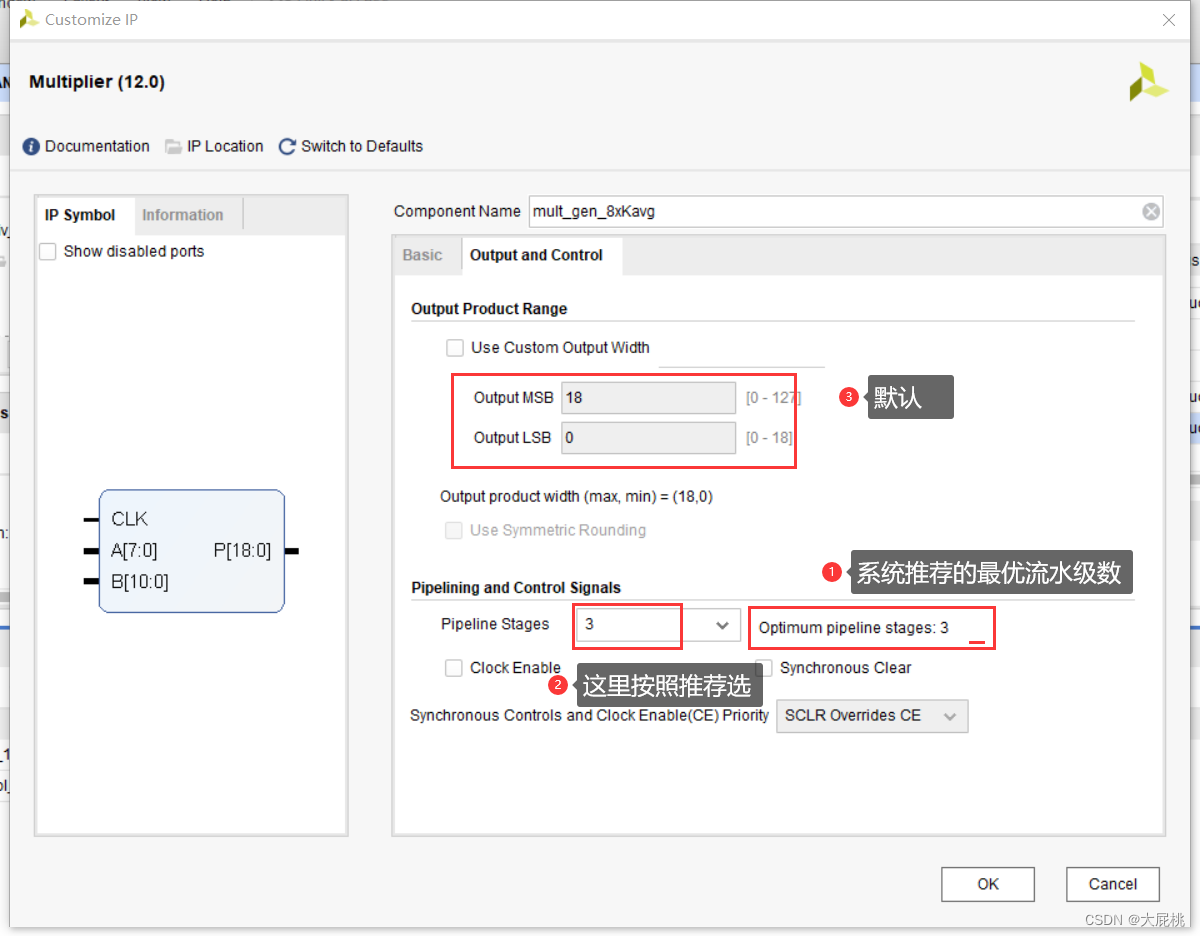

基于 Zynq+AD+DA 的振动台控制器FPGA算法实现(三)

4 振动台控制算法的 FPGA 实现 4.1 PID 控制算法 4.1.1 增量式 PID 控制算法 PID 控制为控制工程中经常使用的控制方法[33],其基本原理框图如图 4.1 所 示,其中𝑢𝑢(𝑡𝑡)为控制信号、𝑟&#x…

【ZYNQ入门】第十篇、基于FPGA的图像白平衡算法实现

目录

第一部分、关于白平衡的知识

1、MATLAB 自动白平衡算法的实现

1.1、matlab代码

1.2、测试效果

1.3 测试源图

2、为什么摄像头采集的图像要做白平衡

3、自动白平衡算法总结

4、FPGA设计思路

4.1、实时白平衡的实现

4.2、计算流程优化思路

第二部分、硬件实…

Vivado 设计实现时报错The design is empty的解决方案(亲测有效)

[Place 30-494] The design is empty

使用Vivado进行设计实现时,点击Run Implementation,运行过程报错The design is empty,如图所示: 报错原因

因为设计只有输入,synthesis tool 可以优化到什么都没有。换句话说&am…

Vivado使用记录(未完待续)

一、Zynq开发流程 二、软件安装 三、软件使用

字体大小修改:Setting、Font 四、Vivado基本开发流程

1、创建工程 Quick Start 组包含有 Create Project(创建工程)、 Open Project(打开工程)、 Open Example Project&…

ZYNQ连载02-开发环境

ZYNQ连载02-开发环境

1. 官方文档

ZYNQ开发使用的软件为Vivado/Vitis/PetaLinux,软件体积比较大,硬盘保留100G以上的空间,赛灵思提供详细的文档,链接如下: ZYNQ文档

2. Vivido和Vitis安装

赛灵思统一安装程序 3. PetaLinux安装…

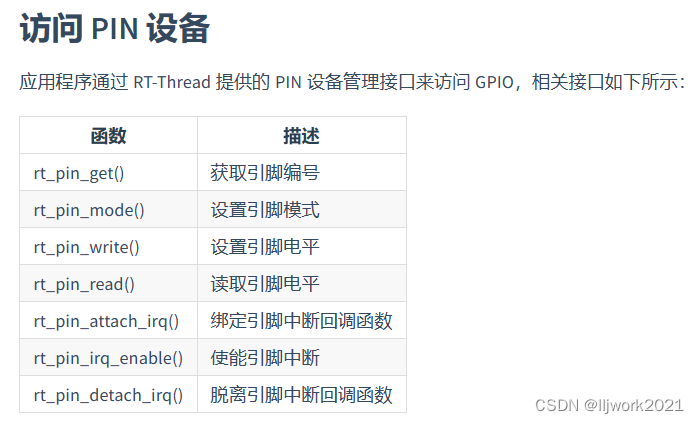

ZYNQ连载07-PIN设备

ZYNQ连载07-PIN设备

1. 简述

RT-Thread PIN设备 这里参看RT-Thread提供的PIN设备管理接口,简单封装了几个接口函数。

2. 实现

#include "include/drv_gpio.h"

#define LOG_TAG "drv_gpio"

static XGpioPs xgpiops;void rt_pin_mode(rt_…

ZYNQ——脉宽调制之呼吸灯实现

文章目录 原理简介实验代码软件仿真板上验证 原理简介

呼吸灯的实现过程就是把不同占空比的脉冲输出后加在LED上,LED灯就会显示不同的亮度,通过不断地调节方波的占空比,LED灯的亮度也会跟着变化,看起来就像是“呼吸”一样。 要得…

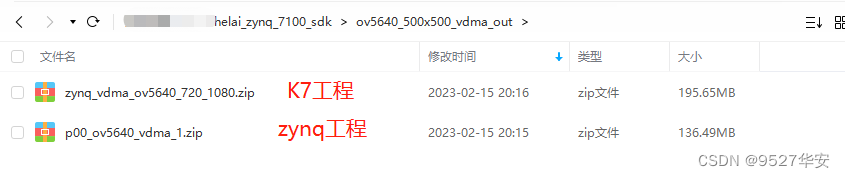

FPGA基于VDMA实现任意分辨率视频输出显示,高度贴近真实项目,提供工程源码和技术支持

目录1、前言2、任意分辨率视频输出理论基础3、VDMA实现数据缓存4、工程1:Kintex7使用VDMA5、工程2:Zynq7100使用VDMA6、上板调试验证并演示7、福利:工程代码的获取1、前言

之前写过一篇FPGA纯verilog实现任意分辨率视频输出显示,…

Zynq-7000系列FPGA使用 Video Processing Subsystem 实现图像缩放,提供工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐FPGA图像处理方案FPGA图像缩放方案自己写的HLS图像缩放方案 3、设计思路详解Video Processing Subsystem 介绍 4、工程代码详解PL 端 FPGA 逻辑设计PS 端 SDK 软件设计 5、工程移植说明vivado版本不一致处理FPGA型号不一致处理其他注意事项…

Zynq UltraScale+ XCZU3EG 纯VHDL解码 IMX214 MIPI 视频,2路视频拼接输出,提供vivado工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优越性4、详细设计方案设计原理框图IMX214 摄像头及其配置D-PHY 模块CSI-2-RX 模块Bayer转RGB模块伽马矫正模块VDMA图像缓存Video Scaler 图像缓存DP 输出 5、vivado工程详解PL端FPGA硬件设计…

【zedboard找不到COM串口bug】驱动下载地址

今天在使用zedboard过程中出现了sdk终端没有COM串口的问题: 解决方法见【zedboard串口bug最终解决办法】zynq开发 在SDK 终端Teminal找不到COM3、COM5等接口 无法连接uart串口 ZYNQ驱动问题 解决办法_https://blog.csdn.net/taneeyo/article/details/1149_Taneeyo的…

ZC706+AD9361 运行 open WiFi

先到github上下载img,网页链接如下:

https://github.com/open-sdr/openwifi?tabreadme-ov-file 用win32 Disk lmager 把文件写入到SD卡中,这一步操作会把SD卡重新清空,注意保存数据。这个软件我会放在最后的网盘链接中 打开linu…

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(后记)

2024.03.05:

测试了开发板网线直连电脑可以传输数据。但是通过开发板→交换机→电脑,没有数据传输过去。通讯采用UDP通讯。首先是UDP传输不可靠,有可能存在丢包、包先后顺序有问题,这就无法满足后续对采集数据的傅里叶变换和傅里…

ZYNQ7000 FSBL加载启动代码详解

参考资料:

https://blog.csdn.net/zhaoxinfan/article/details/54958641

https://blog.csdn.net/asmartkiller/article/details/84072643

https://blog.csdn.net/qq_40155300/article/details/89001808 SDK版本:2017.4 写在前面:

该文档不…

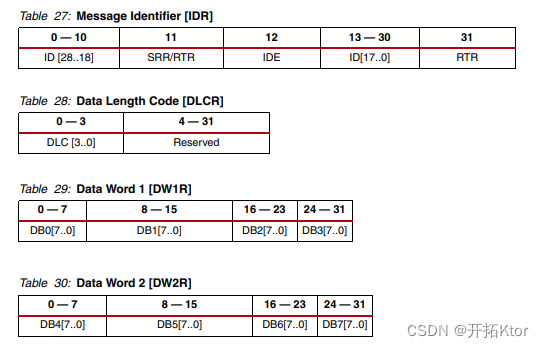

ZYNQ:串口-CAN协议转换

前言

目前已经实现zynq的PS-CAN和PL-CAN功能。串口-CAN协议转换是实现以太网-CAN功能的过渡,通过这个流程能够减少后期以太网工程出现问题的频率。阶段性功能目标如下:

实现数据在CAN调试助手和串口调试助手之间的来回转换,从而了解中断机制…

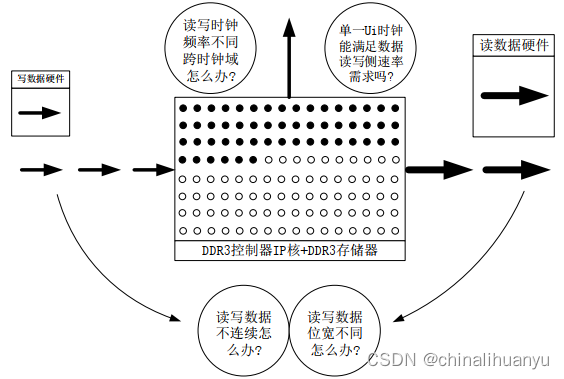

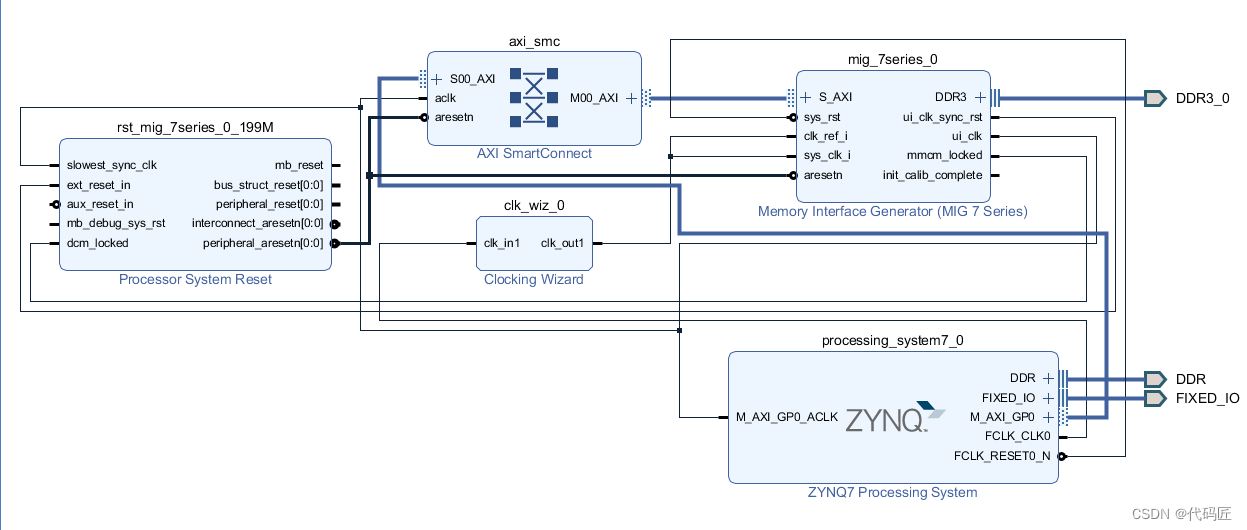

ZYNQ7035 PS读写PL端DDR3

ZYNQ7035 PS读写PL端DDR3

硬件平台

小熊猫嵌入式电子:ZYNQ7035_R5

MIG IP核配置 PL端DDR管脚分配

NET "ddr3_addr[0]" LOC "A8" | IOSTANDARD SSTL15 | VCCAUX_IO NORMAL ;NET "ddr3_addr[…

ZYNQ连载03-Vivado创建工程

ZYNQ连载03-Vivado创建工程

1. 硬件参数

名称参数主控xc7z020clg400-2DDRMT41J256M16RE-125

2. 创建工程 3. 串口配置 4. DDR配置 5. SD配置 6. ETH配置 7. USB配置 8. 导出硬件

Generate Output ProductsCreate HDL WrapperExport Hardware Platform 执行以上步骤后&#…

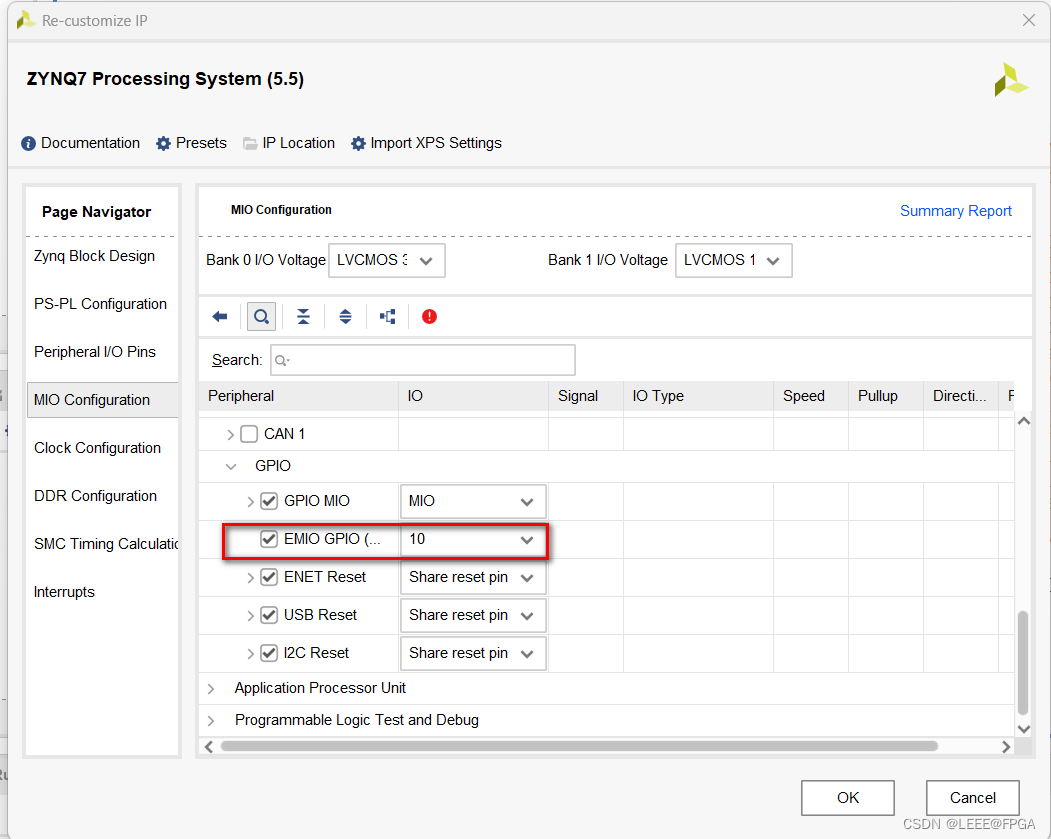

ZYNQ_SDK EMIO

ZYNQ_SDK EMIO

PS 和外部设备之间的通信主要是通过复用的输入/输出(Multiplexed Input/Output,MIO)实现的。除此之外,PS 还可以通过扩展的 MIO(Extended MIO,EMIO)来实现与外部设备的连接。

E…

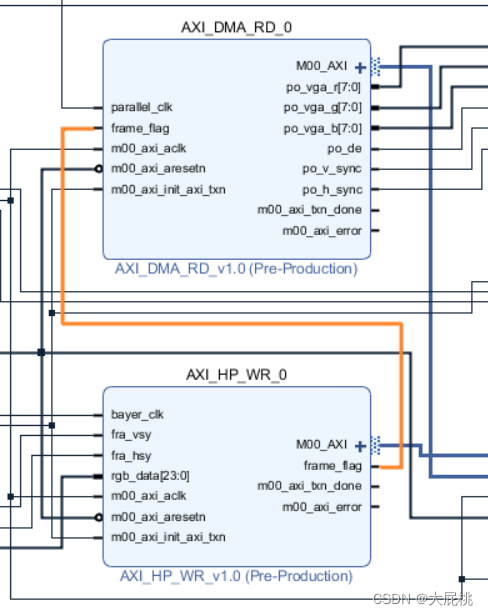

【ZYNQ入门】第九篇、双帧缓存的原理

目录

第一部分、基础知识 1、HDMI视频撕裂的原理

2、双帧缓存的原理

第二部分、代码设计原理

1、AXI_HP_WR模块

2、AXI_HP_RD模块

3、Block design设计

第三部分、总结

1、写在最后

2、更多文章 第一部分、基础知识 1、HDMI视频撕裂的原理 在调试摄像头的时候…

ZYNQ之FPGA学习----Vivado软件使用

1 Vivado软件使用

Vivado Design Suite 是 Xilinx 公司的综合性 FPGA 开发软件,可以完成从设计输入到硬件配置的完整FPGA 设计流程。Vivado学习使用版本为Vivado v18.3

Vivado软件使用流程:

新建工程设计输入分析与综合约束输入设计实现生成和下载比特…

zynq基于XDMA实现PCIE X8视频采集HDMI输出 提供工程源码和QT上位机程序和技术支持

目录 1、前言2、我已有的PCIE方案3、基于zynq架构的PCIE4、总体设计思路和方案视频输入通路PCIE数据缓存通路视频输出通路 5、vivado工程详解6、SDK 工程详解7、驱动安装8、QT上位机软件9、上板调试验证10、福利:工程代码的获取 1、前言

PCIE(PCI Expre…

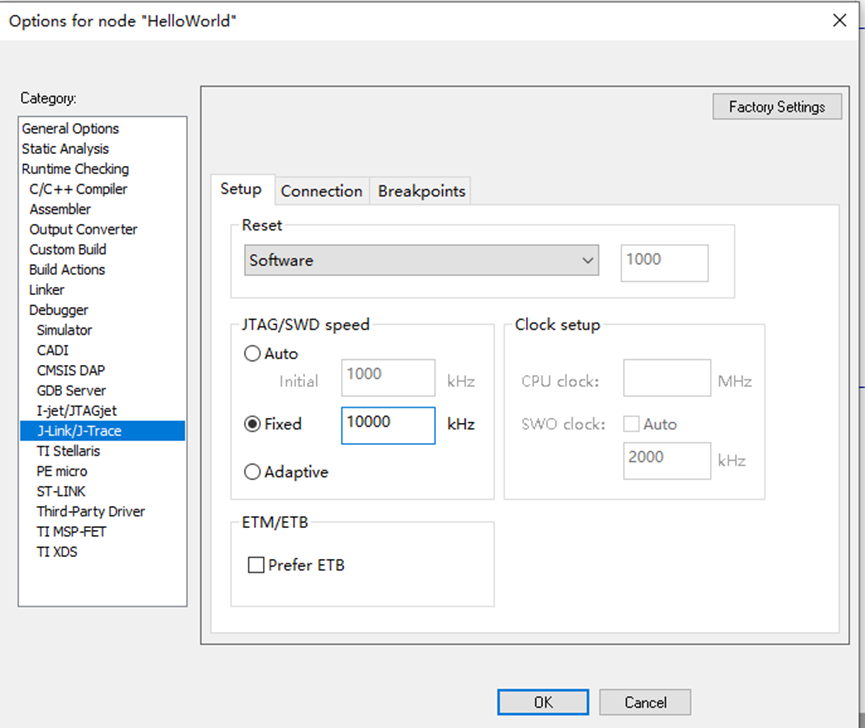

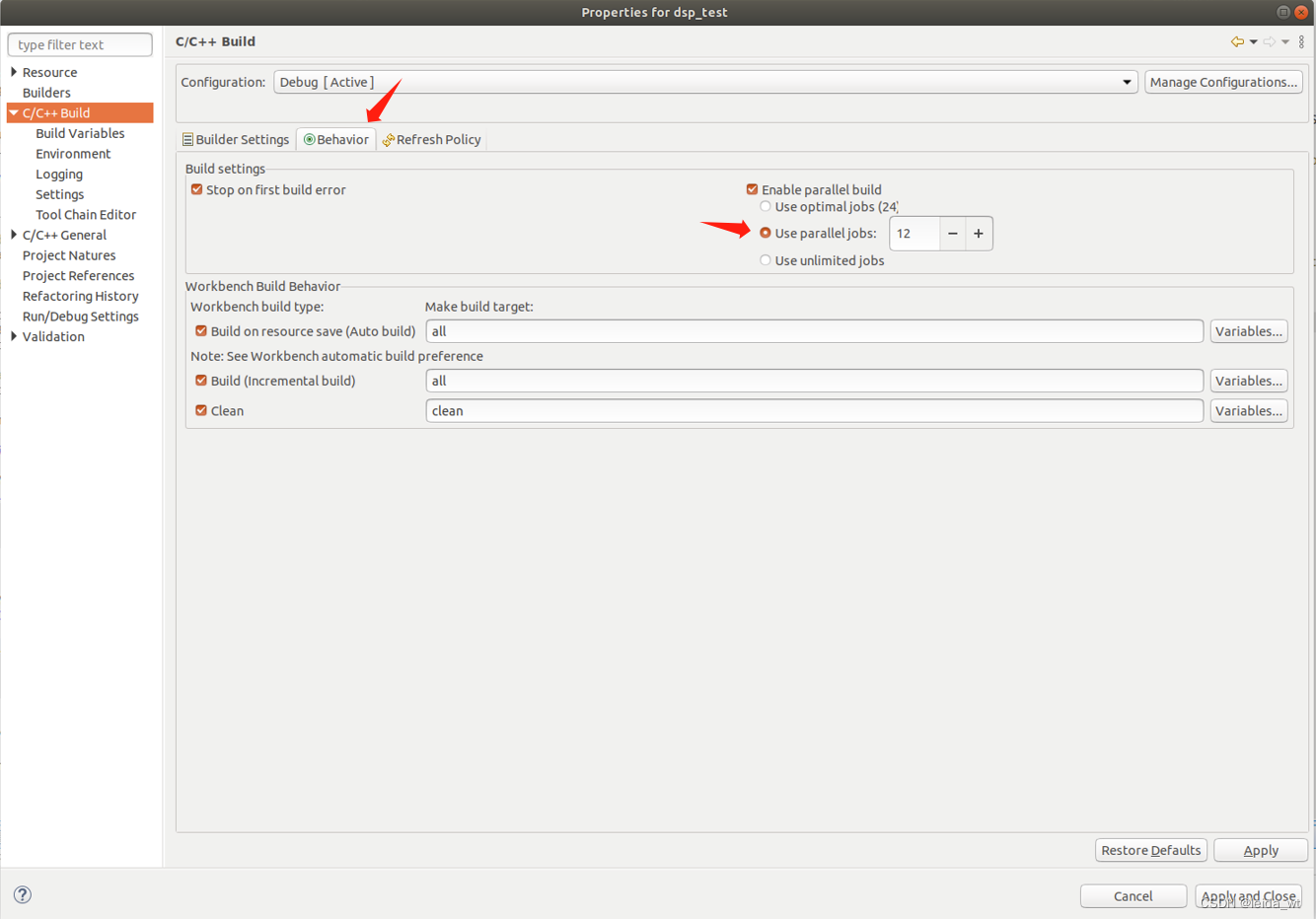

ZYNQ移植ARM CMSIS_DSP库

移植方法

Vitis中新建一个Application Project,选择HelloWord模板。按下面步骤移植CMSIS_DSP:

下载CMSIS_DSP,拷贝如下文件夹到Vitis工程: SourceIncludePrivateIncludeComputeLibrary (only if you target Neon) 对Source路径下…

AXI-Stream协议详解(3)—— AXI4-Stream IP核原理分析

一、前言 在之前的文章中,我们介绍了AXI-S协议的一些基础知识,这是我们进行本文学习的前置基础,因此建议在开始本文章的学习前,完整阅读以下两篇文章:

AXI-Stream协议详解(1)—— Introduction…

江山易改本性难移之ZYNQ SDK QSPI固化bug及其解决方法

之前在Vivado2018.3通过QSPI方式固化程序时出现问题,显示flash擦除成功,但最后总是不能写入到flash中。 查资料发现从VIVADO 2017.3版本开始,Xilinx官方为了使Zynq-7000和Zynq UltraScale 实现流程相同,在QSPI FLASH使用上做了变化…

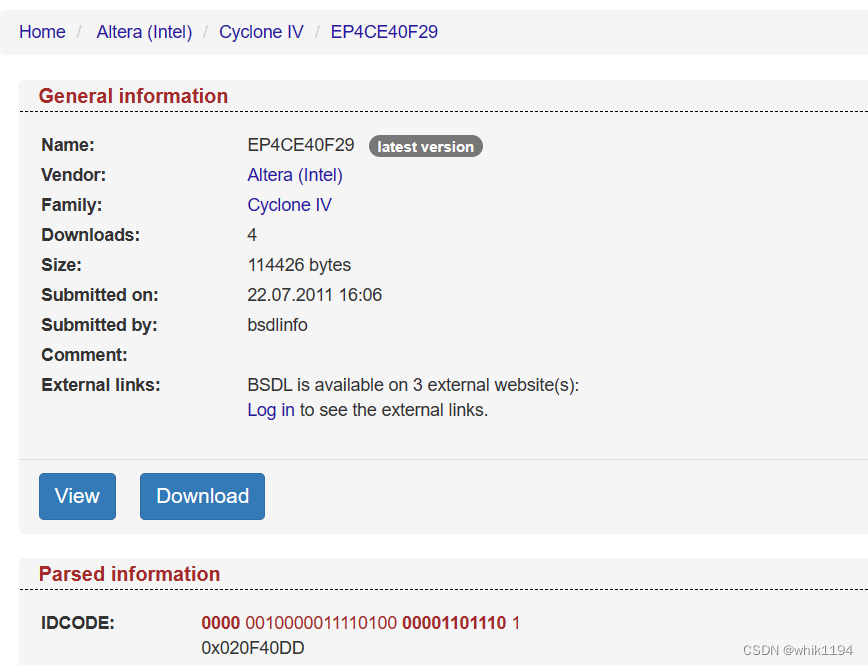

获取Xilinx FPGA芯片IDCODE的4种方法(支持任何FPGA型号)

文章目录 方式1:官方文档方式2:一个头文件方式3:BSDL文件方法4:芯片IDCODE在线搜索网站Xilinx FPGA部分型号IDCODE汇总 方式1:官方文档

对于常用的Spartan-6系列可以在UG380文档中找到对应的IDCODE,Sparta…

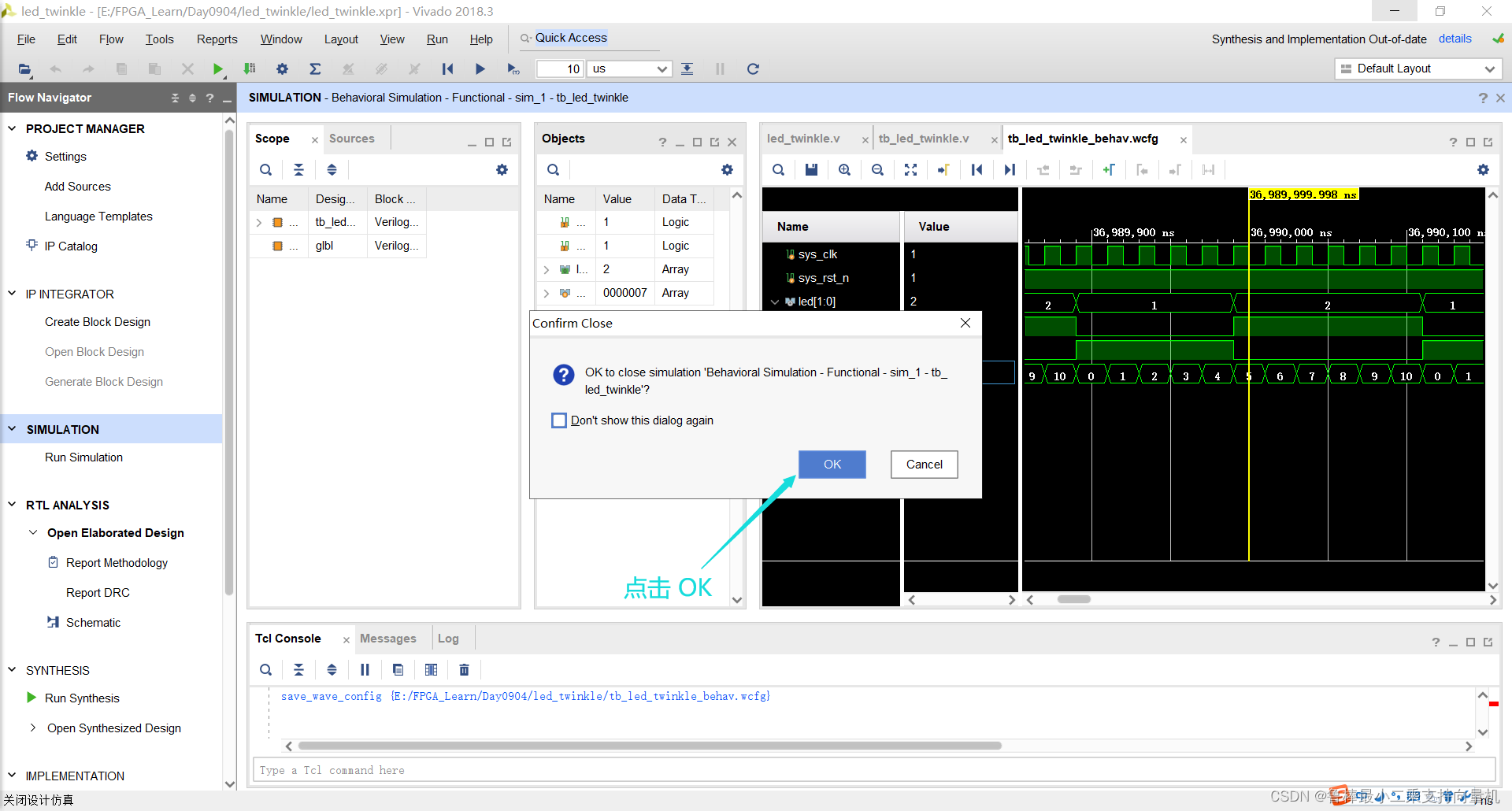

ZYNQ之FPGA学习----Vivado功能仿真

1 Vivado功能仿真

阅读本文需先学习: FPGA学习----Vivado软件使用

典型的FPGA设计流程,如图所示: 图片来自《领航者ZYNQ之FPGA开发指南》

Vivado 设计套件内部集成了仿真器 Vivado Simulator,能够在设计流程的不同阶段运行设计的功能仿真和…